### University of Nebraska - Lincoln

# DigitalCommons@University of Nebraska - Lincoln

Patents Held by Members of the Department of Chemical and Biomolecular Engineering Chemical and Biomolecular Engineering Research and Publications

5-5-1998

# Direct chip attachment (DCA) with electrically conductive adhesives

Ravi F. Saraf University of Nebraska-Lincoln, rsaraf2@unl.edu

Follow this and additional works at: https://digitalcommons.unl.edu/chemengpatent

Part of the Chemical Engineering Commons

Saraf, Ravi F., "Direct chip attachment (DCA) with electrically conductive adhesives" (1998). *Patents Held by Members of the Department of Chemical and Biomolecular Engineering*. 51. https://digitalcommons.unl.edu/chemengpatent/51

This Article is brought to you for free and open access by the Chemical and Biomolecular Engineering Research and Publications at DigitalCommons@University of Nebraska - Lincoln. It has been accepted for inclusion in Patents Held by Members of the Department of Chemical and Biomolecular Engineering by an authorized administrator of DigitalCommons@University of Nebraska - Lincoln.

US005747101A

## United States Patent [19]

#### Booth et al.

#### [54] DIRECT CHIP ATTACHMENT (DCA) WITH ELECTRICALLY CONDUCTIVE ADHESIVES

- [75] Inventors: Richard B. Booth, Williamson County. Tex.; Michael A. Gaynes; Robert M. Murcko, both of Broome County, N.Y.; Viswanadham Puligandla, Travis County, Tex.; Judith M. Roldan; Ravi Saraf, both of Westchester County, N.Y.; Jerzy M. Zalesinski, Crittenden County, Vt.

- [73] Assignce: International Business Machines Corporation, Armonk, N.Y.

- [21] Appl. No.: 630,033

- [22] Filed: Apr. 9, 1996

#### **Related U.S. Application Data**

- [63] Continuation of Ser. No. 190,507, Feb. 2, 1994, Pat. No. 5,543,585.

- [51] Int. Cl.<sup>6</sup> ...... B05D 5/12

- [52] U.S. Cl. ...... 427/96; 427/97; 427/282;

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

4,600,600 7/1986 Pammer et al. ..... 437/183

[11] Patent Number: 5,747,101

## [45] Date of Patent: May 5, 1998

| 4,604,644 | 8/1986  | Beckham et al 257/738  |  |

|-----------|---------|------------------------|--|

| 5,086,558 | 2/1992  | Grube et al.           |  |

| 5,124,781 | 6/1992  | Tashiro 257/759        |  |

| 5,356,838 | 10/1994 | Kim 437/183            |  |

| 5,550,408 | 8/1996  | Kunimoto et al 257/737 |  |

| 5,583,747 | 12/1996 | Baird et al 257/738    |  |

#### FOREIGN PATENT DOCUMENTS

| 1-226161 | 9/1989 | Japan . |

|----------|--------|---------|

| 3-209840 | 9/1991 | Japan . |

| 4-042550 | 2/1992 | Japan . |

Primary Examiner-Shrive Beck

Assistant Examiner—Brian K. Talbot Attorney, Agent, or Firm—Whitham, Curtis, Whitham & McGinn; Arthur J. Samodovitz

#### [57] ABSTRACT

A simple process for card assembly by Direct Chip Attachment (DCA) uses electrically conductive adhesives. Two methods create the same intermediate wafer product with a layer of insulative thermoplastic and conductive thermoplastic bumps. After sawing or dicing the wafer to form the chips, the chips are adhered to chip carriers with conductive pads which match the conductive thermoplastic bumps, using heat and pressure. Chips may be easily removed and replaced using heat.

#### 15 Claims, 8 Drawing Sheets

# METHOD I

FIG.4

## METHOD II

10

45

65

#### DIRECT CHIP ATTACHMENT (DCA) WITH ELECTRICALLY CONDUCTIVE ADHESIVES

This application is a continuation of application Ser. No. 08/190,507, filed on Feb. 2, 1994 now U.S. Pat. No. 5.543, 5 585.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention generally relates to the manufacture of electronic circuits and, more particularly, to a module structure and a simple process for card assembly by Direct Chip Attachment (DCA). using electrically conductive adhesives, which are reworkable.

1. Background

An involved card assembly attach process exists for Direct Chip Attachment (DCA). Unique decals are fabricated with a plated solder pattern corresponding to the chip pad footprint. These decals are accurately positioned onto 20 the intended footprint of the chip carrier and the solder is subsequently transferred to the carrier sites in a reflow oven. The soldered pads are then leveled mechanically for coplanarity and finally the chips are placed and reflowed.

Solder alloys are used pervasively to interconnect com- 25 ponents to carriers. Undesirable attributes of solder alloys include high temperature joining, cleaning/residues, fatigue life and the environmental ramification of lead (Pb).

Moore et al., U.S. Pat. No. 5,120,678, disclose a method for assembling an integrated circuit component to a substrate 30 with insulative and conducting thermoplastic; by a solder by interconnection that is reinforced by a polymer film. While this method encapsulates ball grid arrays with a thermoset adhesive, the thermoset is not reworkable.

An alternative to solder DCA is electrically conductive <sup>35</sup> adhesive joining. Screen printing 0.004" features on 0.008" centers is possible with some electrically conductive adhesives.

U.S. Pat. Nos. 5.074,947 to Estes and 5.086.558 to Grube, disclose attaching flip chips to substrates using conductive polymer materials. All the above cited patents are incorporated herein by reference.

#### SUMMARY OF THE INVENTION

It is therefore an object of the present invention to provide a process to attach a flip-chip to a substrate using a thermoplastic, isotropically conducting adhesive.

According to a preferred embodiment of the invention. there is provided a two pass screen process in which a 50 thermoplastic adhesive is applied to the pad side of the wafer. This two pass process can be accomplished in either of two methods where, in one pass, an electrically conductive thermoplastic adhesive is applied to the chip bond pads. A second pass applies an electrically insulating thermoplas- 55 tic adhesive to the non-conductive area of the same wafer surface. The methods differ primarily by the order of the passes.

In a second preferred embodiment of this invention, individual chips are heated to a temperature at which the 60 thermoplastic adhesive is in a tacky state, in preparation for bonding to a substrate. Placement and bonding is accomplished in one step. The electrical pads on the chip and substrate are interconnected with the electrically conductive adhesive.

It is further an object of the present invention to provide a method of preparing a wafer for DCA bonding with

electrically conductive adhesives using current art in adhesive application.

The assembly process is a one step process which accomplishes placement, joining and encapsulation and which is reworkable. The process eliminates the need for many of the commonly required steps to prepare chip sites on the substrate for DCA. The process also eliminates the need for solder reflows, two flux application, post attach cleaning. application and cure of thermoset encapsulant.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The foregoing and other objects, aspects and advantages will be better understood from the following detailed description of a preferred embodiment of the invention with <sup>15</sup> reference to the drawings, in which:

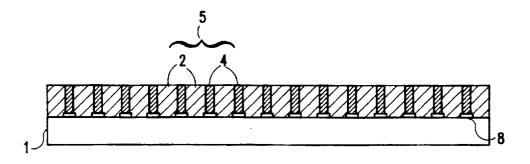

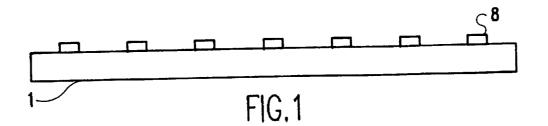

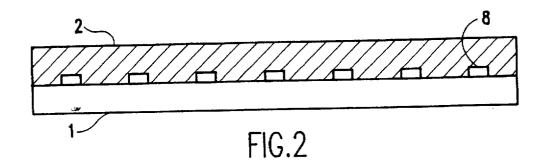

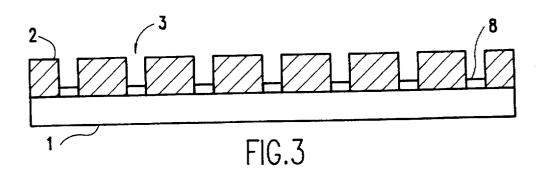

FIGS. 1, 2 and 3 show cross-sectional views of a substrate in the process of adding insulative and conducting thermoplastic to the substrate, according to the first method of the invention;

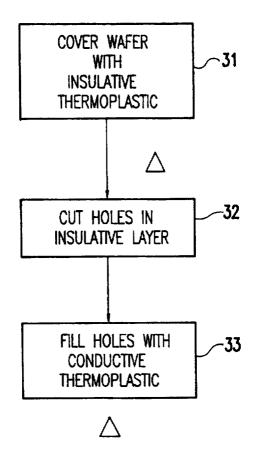

FIG. 4 is a flow diagram showing the process steps of the first method;

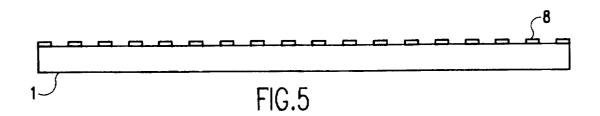

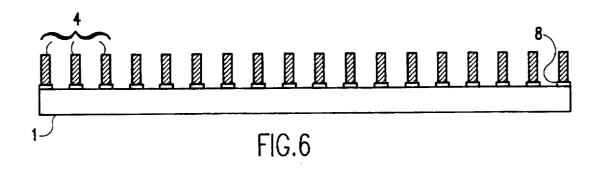

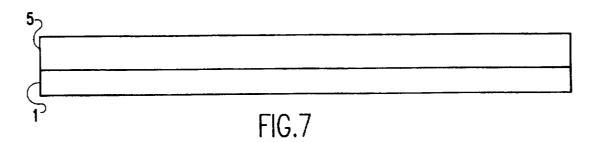

FIGS. 5, 6 and 7 show cross-sectional views of a substrate in the process of adding insulative and conducting thermoplastic to the substrate, according to the second method of the invention:

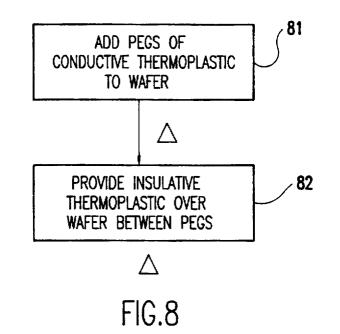

FIG. 8 is a flow diagram showing the process steps of the second method;

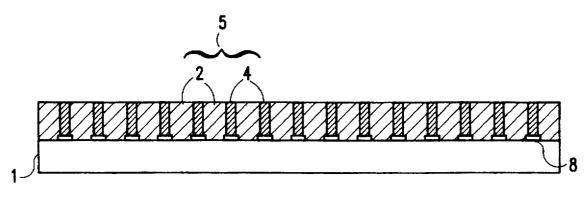

FIG. 9 is a cross-sectional view of a finished substrate

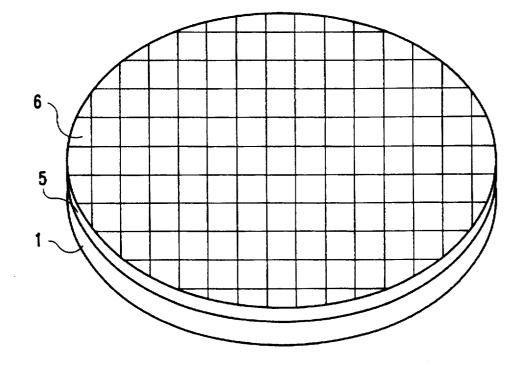

FIG. 10 is a wafer with a thermoplastic layer ready for sawing or dicing into chips;

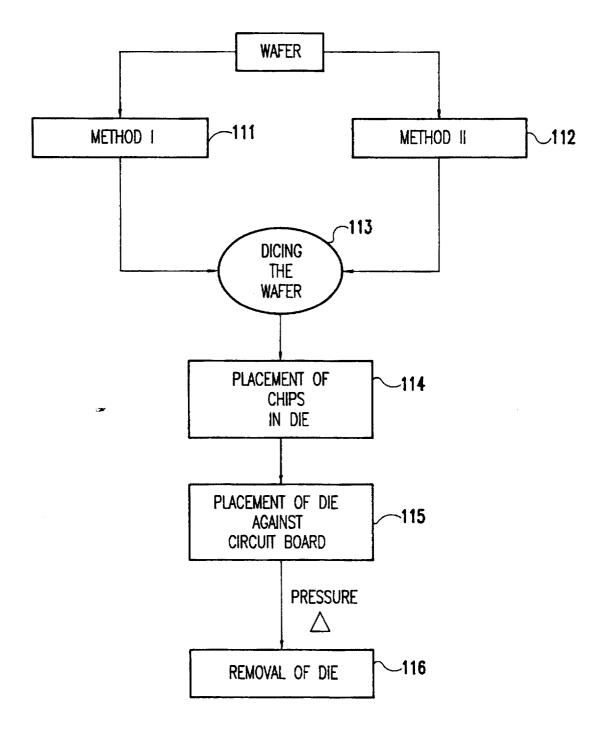

FIG. 11 is a flow diagram showing the process of creating chips by either of the two methods and adding them to a chip carrier;

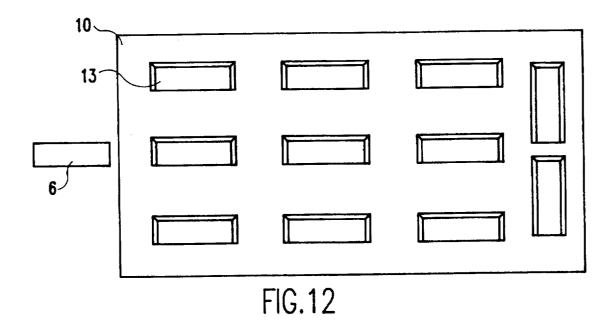

FIG. 12 is a plan view of die for assembling chips on a chip carrier;

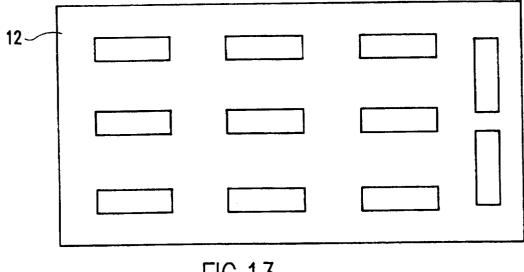

FIG. 13 is a plan view of a chip carrier;

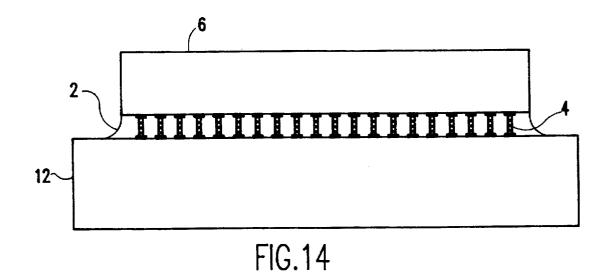

FIG. 14 is a cross-sectional view of a chip adhered to a chip carrier; and

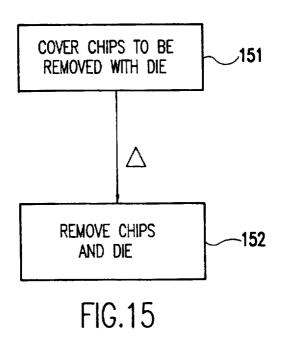

FIG. 15 is a flow diagram of reworking a chip and chip carrier.

#### DETAILED DESCRIPTION OF A PREFERRED EMBODIMENT OF THE INVENTION

Referring now to the drawings, and more particularly to FIG. 1, there is shown a substrate 1. The substrate may be a wafer or chip with integrated circuits or a substrate (ceramic, organic, or flexible) to which an integrated circuit chip is to be attached, such as a chip carrier module or a circuit board/card. In a specific embodiment, a wafer, prior to the practice of the first method according to the invention. has a plurality of chip sites at which integrated circuits have been formed. Each chip site includes a matrix of thin conductive metal contacts 8. After the processing according to the invention, the wafer is sawn or diced into the individual chips. In FIG. 2, an insulative thermoplastic adhesive 2 is added to the surface of substrate 1 where the contact pads 8 are located. After baking or heating the insulative adhesive 2, holes 3 are made in the adhesive layer 4, as shown in FIG. 3. The holes 3 may be made in the insulative adhesive layer 2 at each metallic pad by various methods including:

1. spin coating onto the substrate 1, drying, and then. using laser oblation of the adhesive material in pad areas 8 to make the holes

10

65

- 2. bonding a dry insulative adhesive film which is prepunched with holes 3 directly to the substrate 1 (a stiff backing may be required during punching), or

- 3. screen printing to place insulative adhesive everywhere on the substrate surface except chip bond pads 8 and 5 then drying. The holes 3 are then filled with conductive thermoplastic adhesive and baked or heated at an elevated temperature such as 80°-150° C. and preferably at about 120° C. to dry the conductive adhesive.

FIG. 4 shows a flow diagram of the first method. The first step 31 is to coat the substrate with the insulative adhesive, and after curing, holes are cut in the insulative layer in step 32. Finally, the holes are filed with a conductive adhesive in step 33, and the conductive adhesive is dried.

FIGS. 5 through 7 illustrate the second method according to the invention. FIG. 5 shows a cross-sectional view of the substrate 1 with conductive metal pads 8, prior to processing. In FIG. 6, conductive adhesive bumps or pegs 4 are added to the substrate 1. Preferably, the bumps are applied by mask screening. The conductive thermoplastic may also be added to a matrix of conductive metal pads 8 on another 20 substrate to which the first substrate is to be attached to assist in bonding. The conductive thermoplastic is then dried. Insulative adhesive 2 is applied to the wafer between conductive adhesive 4 bumps or pegs to create the composite structure 5 which covers the entire surface of the substrate, 25 as shown in FIG. 7. Prior to adding insulative adhesive paste, the conductive bumps may be plated (electroless, electroplate, or evaporation) with a very thin layer of low melting temperature metal such as Ag to prevent interaction with the insulative adhesive (e.g. dissolving the pegs). This 30 product is baked to dry the insulative thermoplastic.

Prior to applying the insulating adhesive, there may be a layer of solder resist (procoat) on the substrate such as PSR-4000 or VACREL. Also, there may be a passivation layer on the chip such as polyimide or nitride. The insulative 35 adhesive must be compatible with these chip and carrier surfaces in order to reliably bond the chip to the carrier substrate with the single layer of adhesive.

In this second method, the insulative adhesive may be applied by bonding a prepunched film, screen printing, or 40 spreading a flowable paste or emulsion (e.g. spin coating) directly onto the substrate surface.

FIG. 8 shows a flow diagram of the second method. The first step 81 is to add pegs of conductive thermoplastic adhesive to chip pad sites on the wafer. Then, in step 82, the 45 insulative layer of adhesive is provided around the pegs.

FIG. 9 is a cross-sectional view of the final product, whether produced by the first or second methods. As can be seen in this view, the conductive adhesive 4 is surrounded by the insulative adhesive 2, and the composite adhesive struc- 50 method, here indicated as Method I and denoted by referture 5 covers the entire surface of the substrate. At this stage, the conductive adhesive may project up above the level of the surrounding insulative adhesive and the holes may have a larger diameter than the bumps or pegs of conductive adhesive, but the volume of the conductive adhesive should 55 be about the same as the holes, so that upon attachment, the two adhesives completely fill the space between the chip and substrate. FIG. 10 illustrates a wafer 1, with a composite thermoplastic layer 5 ready to be sawn or diced into chips 6. The thickness of the thermoplastic adhesives must be suf- 60 ficient to compensate for any bowing of the substrates (such as an FR-4 circuit board), and metal pad height to 1 arances, and to form a good void free bond. Preferably, the thickness is 1-5 mils for ceramic and flexible substrates and 3-8 mil to attach chips to organic substrates, such as FR-4.

As can be understood from the foregoing, chips in the wafer are formed with an electrically conductive adhesive in 4

a two pass screen process to apply adhesive to the pad side of the wafer. The order of the steps is not controlling. The first pass applies either the insulative or conductive adhesive to the chip bond pads. The second screening would apply the same or similar adhesive paste with a conductive or insulative filler to the same substrate surface. The addition of insulative filler to the insulative adhesive is optional depending on coefficient of thermal expansion (CTE) requirements. After each screening, solvent would be driven off in a bake or vacuum/bake step. The completed wafer is then ready for dicing.

The insulative thermoplastic adhesive is a dry fully polymerized dielectric adhesive preferably selected from one of the following polymer systems and may be filled with dielectric solids preferably ceramic particles, quartz, or 15 glass. Preferred dielectric polymer systems include thermoplastic polymers, copolymers, or blends. Examples of polymers include, but are not limited to, nylons, polysulfones, polyesters, flexible and soluble polyimides and siloxanes. Copolymers include, but are not limited to, random, segmented or block copolymers made of ethylene and vinyl acetate (EVA), siloxane and aryl-ethers, polyurethanes composed of polyisocyanate and polyethers or polyester segments. Blends may be of two or more polymers/copolymers such as ethylene-acrylate copolymer with polyethylene, EVA and poly(vinyl chloride) (PVC), polyester and PVC. Conductive thermoplastic systems are composed of fully polymerized thermoplastic systems such as the above and electrically conductive particles made of or coated by Au, Ag, Pd or their oxide free, noble alloys. In order to form a paste for application the fully polymerized thermoplastic system and fillers are thinned with a solvent or mixed a liquid to form an emulsion. After application the material is heated at an elevated temperature to evaporate the solvant or liquid until dry (non-tacky). In order to bonds the chip to the substrate the adhesive must be heated significantly above the transition temperature until it becomes tacky. The insulating and conductive adhesive materials are preferably selected to be compatible during attachment processing. The thermoplastic materials must be chemically compatible so they do not negatively affect each others properties and preferably so that they bond together tightly for strength. Also, preferably the properties of the thermoplastics are similar to provide about the same CTE to minimize stresses and provide overlapping preferred drying and bonding temperature ranges.

FIG. 11 is a flow diagram illustrating preparing a chip to be placed on a chip carrier, starting with a wafer. As can be seen in the diagram, the wafer can be prepared by either ence numeral 111, where insulative thermoplastic adhesive paste is added to the wafer, dried (unless added as a pre-punched dry film adhesive bonded directly to the wafer surface), and then conductive thermoplastic adhesive paste is added to holes made in the insulative adhesive, or Method II and denoted by reference numeral 112, where conductive pegs of adhesive paste are added to the wafer, dried, then the insulative thermoplastic paste is applied to fill gaps between the conductive thermoplastic pegs. Following either Method I or Method II, the wafer is diced into chips in step 113. The chips are placed in a die in step 114, and the die is pressed against a chip carrier and heat is added in step 115. When the die is removed in step 116, the chip remains adhered to the chip carrier. An optional step in this process is to add conductive thermoplastic adhesive to the pads on the chip carrier and drying the optional adhesive before pressing the die and chips against the chip carrier.

Alternative manufacturing methods not illustrated include, applying the insulative adhesive to the chip carrier and the conductive adhesive bumps to the chip. After fitting the matching pieces together, heat and pressure are applied as in other methods. Also, both the insulative and conductive 5 adhesives may be applied to the chip carrier by Methods I and II, using heat and pressure to attach the chip to the prepared chip carrier. Furthermore, the insulative and conductive adhesives may be applied to the chip carrier and in addition, conductive adhesive may be applied to the metal 10 contact pads on the chip.

FIG. 12 illustrates a die 10 which may be used to add chips to a chip carrier 12, illustrated in FIG. 13. Chip carrier 12 will have conductive pads to match the bumps of conductive adhesive 4 in the chip 6 to be adhered to the chip 15 carrier. The chips 6 are placed in recesses 13 on the die. The die 10 is then pressed against the chip carrier 12 and heat is added. When the die is removed, the chips remain adhered to the chip carrier. FIG. 14 shows a single chip adhered to the printed chip carrier after assembly. Here, a chip 14 is 20 adhered to a chip carrier 12 with a layer of insulative thermoplastic adhesive 2 filling gaps between conductive thermoplastic adhesive 4 bumps. The electrically insulating thermoplastic adhesive completely fills the volume between the chip and the chip attach site around the electrically 25 conductive adhesive pegs which adhesively connect between confronting pairs of metal contact pads.

This process simplifies mass production of chips mounted to carriers by removing the need for solder and makes it possible to replace chips since the thermoplastic adhesive is 30 reworkable. Reworking is illustrated in the flow chart depicted in FIG. 15. Because this is a thermoplastic adhesive, reworking is relatively simple and inexpensive. To replace a single chip in a chip carrier, a die to fit the single chip is placed over the chip in step 151. The die is heated and 35 then removed, taking the chip with it in step 152. Any remaining adhesive may require removal using known solvents depending on the adhesive system. A new chip is then placed in a single chip die, pressed against the board with heat, and adhered to the board, much the same as in the 40 original assembly of the printed chip carrier. This is a particularly useful feature of this invention which is not found in other methods of chip to carrier assembly. In other chip attachment technologies, if a single chip of a chip carrier is bad, in most cases the whole must be replaced. In 45 other cases, there is an involved process of filing thermosetting polymers remaining on the chip carrier after removing the bad chip. The process according to the invention makes chip replacement a simple and economically viable 50 process.

A step which may be optional depending on chip size and planarity of the carrier surface would be to screen dispense electrically conductive adhesive onto the carrier pads as well and to dry this adhesive prior to connection (heat bonding).

In preparation for bonding chips to a chip carrier or circuit 55 board, individual chips are heated to a temperature significantly above the transition temperature at which the thermoplastic adhesive is in a soft, tacky state. The surface of the carrier chip site is heated similarly. A typical temperature would be 150° to 300° C. An automatic chip placement tool 60 would be used to pick the chip and place the chip on the chip site of the carrier. Placement and bonding is accomplished in one step. Bonding occurs with time at temperature and pressure. The placement tool can be set to apply the required bonding load (e.g.>30 psi) for the necessary time (e.g. 65 several seconds). The electrical pads of the chip and carrier are interconnected with the electrically conductive adhesive.

The insulative thermoplastic adhesive mechanically joins the chip to the carrier surface.

While the invention has been described in terms of two preferred embodiments, those skilled in the art will recognize that the invention can be practiced with modification within the spirit and scope of the appended claims.

Having thus described our invention, what we claim as new and desire to secure by letters patent is as follows:

1. A method of making integrated circuit chips comprising the steps of:

applying an insulative thermoplastic adhesive paste, over a semiconductor wafer substrate having a plurality of chip sites and integrated circuits communicating with a matrix of conductive metal pads on a major surface of the substrate;

drying the insulative thermoplastic;

- forming holes in the insulative thermoplastic layer at the metal pads;

- filling the holes with a conductive thermoplastic adhesive paste; and

- drying the conductive thermoplastic to form a dry composite adhesive layer dividing the wafer into a plurality of chips after forming the composite layer.

2. The method recited in claim 1 wherein the step of applying an insulative adhesive is performed by spin coating the substrate surface with a adhesive paste and drying, and the step of forming holes in the insulative thermoplastic layer is performed by laser ablation.

3. The method recited in claim 1 wherein the insulative adhesive layer is dried and pre-formed with punched holes and then bonded directly to the chip surface with heat and pressure.

4. The method recited in claim 1 wherein the insulative adhesive layer is applied by emulsion screening to place the adhesive everywhere except chip bond pads, thereby simultaneously performing the steps of applying the adhesive and forming the holes.

5. The method recited in claim 1 wherein the substrate is an integrated circuit wafer having a plurality of chip sites, and further including the step of dividing the wafer into a plurality of chips after drying both thermoplastic adhesives.

6. The method recited in claim 1 wherein the drying steps include heating to a temperature of at least about  $80^{\circ}$  C.

7. The method recited in claim 1 further including the step of heating the substrate to a temperature between about 150°

C. and about 300° C. to bond the adhesives to the substrate.

8. The method recited in claim 1 wherein the holes are

filled with conductive adhesive paste by mask screening. 9. A method of making integrated circuit chips comprising

9. A method of making integrated circuit clips con the steps of:

providing a semiconductor wafer substrate having a plurality of chip sites and integrated circuits communicating with a matrix of conductive metal contact pads on a major surface of the substrate;

depositing conductive thermoplastic adhesive paste bumps on the metal pads;

drying the conductive adhesive;

- applying an insulative thermoplastic adhesive over the substrate surface between the conductive adhesive deposits;

- curing the insulative adhesive to form a dry composite adhesive layer; and

- dividing the wafer into a plurality of chips after forming the composite layer.

10. The method recited in claim 9 wherein the step of applying the insulative adhesive is performed by emulsion screening of adhesive paste.

11. The method recited in claim 9 wherein the step of applying the insulative adhesive is performed by forming the insulative adhesive into a film, dried, punched and bonded directly to the chip surface by heat and pressure.

12. The method recited in claim 9 wherein the step of 5 applying the insulative adhesive is performed by flowing adhesive paste over spaces between the conductive thermoplastic bumps.

13. The method recited in claim 9 further comprising the step of plating the conductive adhesive bumps with a layer 10 of conductive metal prior to applying an insulative adhesive paste.

14. A method of preparing substrates for attachment comprising the steps of:

providing a first semiconductor wafer substrate having a <sup>15</sup> adhesive on the pads. plurality of chip sites with a matrix of conductive metal pads on a major surface;

depositing an electrically conductive thermoplastic adhesive paste on the metal pads;

depositing an electrically insulating thermoplastic adhesive on the substrate surface around the metal pads;

drying the paste; and

dividing the semiconductor wafer into a plurality of individual chips after said depositing steps and said drying step.

15. The method recited in claim 14 wherein the electrically insulating adhesive is deposited on the substrate as a paste followed by the additional step of drying the insulating adhesive prior to the step of depositing the conductive adhesive on the pads.

\* \* \* \* \*