# University of Nebraska - Lincoln DigitalCommons@University of Nebraska - Lincoln

Stephen Ducharme Publications

Research Papers in Physics and Astronomy

12-1-2009

## Modeling of metal-ferroelectric-insulatorsemiconductor structures based on Langmuir–Blodgett copolymer films

Timothy J. Reece *University of Nebraska*, reecet@unlserve.unl.edu

Stephen Ducharme *University of Nebraska*, sducharme1@unl.edu

Follow this and additional works at: http://digitalcommons.unl.edu/physicsducharme

Part of the Condensed Matter Physics Commons, and the Polymer and Organic Materials

Commons

Reece, Timothy J. and Ducharme, Stephen, "Modeling of metal-ferroelectric-insulator-semiconductor structures based on Langmuir–Blodgett copolymer films" (2009). *Stephen Ducharme Publications*. Paper 58. http://digitalcommons.unl.edu/physicsducharme/58

This Article is brought to you for free and open access by the Research Papers in Physics and Astronomy at DigitalCommons@University of Nebraska - Lincoln. It has been accepted for inclusion in Stephen Ducharme Publications by an authorized administrator of DigitalCommons@University of Nebraska - Lincoln.

# Modeling of metal-ferroelectric-insulator-semiconductor structures based on Langmuir-Blodgett copolymer films

Timothy J. Reece<sup>a)</sup> and Stephen Ducharme<sup>b)</sup>

Department of Physics and Astronomy, Nebraska Center for Materials and Nanoscience,

University of Nebraska, Lincoln, Nebraska 68588-0111, USA

(Received 17 September 2009; accepted 8 November 2009; published online 22 December 2009)

Among the ferroelectric thin films used in field-effect transistor devices; the ferroelectric copolymer of polyvinylidene fluoride (PVDF) ( $-CH_2-CF_2-$ ), with trifluoroethylene (TrFE) ( $-CHF-CF_2-$ ), has distinct advantages, including low dielectric constant, low processing temperature, low cost, and compatibility with organic semiconductors. The operation of a metal-ferroelectric-insulator-semiconductor structure with P(VDF-TrFE) as the ferroelectric layer was analyzed and optimized by numerical solution of the Miller and McWhorter model. A model device consisting of 20 nm PVDF/TrFE on a 10-nm-thick high-k dielectric buffer exhibits a memory window of 5 V with an operating voltage of  $\pm 15$  V. The operating voltage can be reduced to  $\pm 12$  V by reducing the ferroelectric and dielectric thicknesses to 10 and 5 nm, respectively. © 2009 American Institute of Physics. [doi:10.1063/1.3271581]

#### I. INTRODUCTION

A promising material class for use in nonvolatile memories consists of ferroelectric polymers, such as polyvinylidene fluoride (PVDF, consisting of C<sub>2</sub>H<sub>2</sub>-C<sub>2</sub>F<sub>2</sub> monomers) and its copolymers with trifluoroethylene (-CHF-CF<sub>2</sub>-). The VDF copolymers have a large spontaneous polarization, approximately 0.1 C/m<sup>2</sup>, excellent polarization stability, and switching times as short as 25 ns.<sup>2</sup> Their high resistivity of up to 1000  $\Omega$  cm means low leakage, suitable for nondestructive readout applications. Furthermore, they do not require high-temperature processing, have outstanding chemical stability, low fabrication costs, and are nontoxic. Ferroelectric polymers have been incorporated into nonvolatile memory devices, such as metalferroelectric-insulator-semiconductor (MFIS, see Fig. 1 inset) capacitors and ferroelectric field-effect transistor (Fe-FET) structures, in both spun film<sup>3-5</sup> and Langmuir-Blodgett (LB) form.<sup>6,7</sup>

Miller and co-workers<sup>8,9</sup> provided a useful model for the device characteristics of MFIS and Fe-FET structures by combining the charge-sheet model for the semiconductor surface potential<sup>10</sup> with a *tanh* function representation of the ferroelectric polarization hysteresis.<sup>11</sup> This model provides insight into the nonlinear and hysteretic interplay between the polarization state of the ferroelectric and the surface charge of the semiconductor to illustrate, for example, the importance of high doping to achieve high polarization remanence after biasing the semiconductor into strong inversion,<sup>12</sup> and how minor hysteresis loops in the ferroelectric result in different device state paths.<sup>13</sup> The Miller–McWhorter model has previously been applied to model MFIS (Ref. 14) and Fe-FET (Ref. 15) structures containing oxide ferroelectrics such as lead zirconate-titanate. The

#### II. SUMMARY OF THE MODEL

The electrostatic model for the MFIS capacitor structure (Fig. 1 inset) is obtained from Maxwell's equations, the constitutive relations for each layer, and appropriate boundary conditions. For all layers, the electric field E and the electric potential  $\phi$  are related by  $E=-\nabla \phi$ , where the total potential drop across the device, the gate bias voltage, is

$$V_G = \Phi_{\rm MS} - \frac{\sigma_S}{C} - \frac{P_f d_f}{\varepsilon_0 \varepsilon_f} + \phi_S, \tag{1}$$

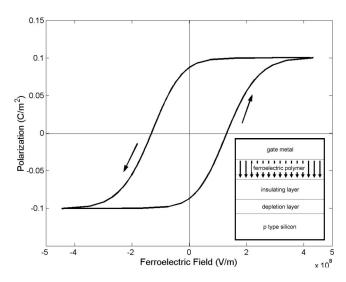

FIG. 1. Polarization-electric field (*P-E*) hysteresis loop for a ferroelectric film modeled from Eq. (3) using parameters listed in Table I. Inset: Structure of an MFIS consisting of a doped silicon wafer, passive oxide layer, ferroelectric layer, and gate electrode.

present work extends this model to ferroelectric polymer LB films, which have very different operating characteristics. <sup>16</sup>

<sup>&</sup>lt;sup>a)</sup>Electronic mail: reecet@unlserve.unl.edu.

b) Electronic mail: sducharme1@unl.edu.

$$C = \left(\frac{d_i}{\varepsilon_0 \varepsilon_i} + \frac{d_f}{\varepsilon_0 \varepsilon_f}\right)^{-1},\tag{2}$$

where  $\phi_S$  is the semiconductor surface potential,  $\sigma_S$  is the semiconductor surface charge,  $P_f$  is the ferroelectric polarization,  $\varepsilon_0$  is the vacuum permittivity,  $\varepsilon_{f,i}$  is the dielectric constant and  $d_{f,i}$  is the thickness of the ferroelectric or insulating layer, and  $\Phi_{\rm MS}$  is the work function difference between the gate metal and the semiconductor.

While the insulating layer is adequately described by a linear dielectric constant (as represented in Eq. (2)), the semiconductor and ferroelectric layers introduce both nonlinearity and hysteresis. The electric displacement of the ferroelectric layer  $D_o = \varepsilon_0 \varepsilon_f E_f + P_f(E)$  consists of contributions from linear polarizability plus the ferroelectric polarization  $P_f(E)$ , which depends on both the magnitude and history of the electric field E. In the case of saturated hysteresis loops, we choose the hyperbolic tangent (tanh) form of the (P-E) hysteresis loop<sup>8,9</sup>

$$P_f(E) = \pm P_S \tanh \left[ \frac{(\pm E - E_C)}{2\delta} \right], \tag{3}$$

where  $P_S$  is the saturation polarization and the loop shape parameter

$$\delta = E_C \left[ \ln \left( \frac{1 + P_R / P_S}{1 - P_R / P_S} \right) \right]^{-1} \tag{4}$$

depends also on the remanent polarization  $P_R$ . The  $\pm$  signs refer to sweeping the field toward negative and positive saturation, respectively. The tanh form of the P-E hysteresis loop (Fig. 1) described by Eq. (2) is a good fit to data from polycrystals and crystals that support a large number of domains during switching.<sup>8</sup>

The semiconductor state is defined by performing an iteration in the surface potential and through the following expression, which relates the silicon surface charge density  $\sigma_S$  to the silicon surface potential  $\phi_S$  through the expression

$$\sigma_{S} = \mp \sqrt{2q_{e}N_{A}\varepsilon_{0}\varepsilon_{S}} \times \left[\sqrt{e^{2\phi_{F}/\phi_{t}}(-\phi_{t}+\phi_{S}+\phi_{t}e^{-\phi_{S}/\phi_{t}})-\phi_{t}-\phi_{S}+\phi_{t}e^{\phi_{S}/\phi_{t}}}\right],$$

(5)

where  $\phi_t = kT/e$ ,  $\varepsilon_S$  is the dielectric constant of the semiconductor,  $N_A$  is the dopant concentration, and  $\phi_F$  is the quasi-Fermi potential

$$\phi_F = \frac{kT}{e} \ln \left( \frac{N_A}{n_i} \right). \tag{6}$$

Saturation of the ferroelectric polarization requires a larger voltage (than in accumulation) because of the potential drop across the depletion layer. <sup>13</sup> The gate voltage required to saturate the ferroelectric film can be determined by noting that the semiconductor potential in the strong inversion mode is twice the Fermi potential,  $\phi_S = 2\phi_F$ .

The recommended device operating voltage would be the minimum gate voltage required to saturate the ferroelec-

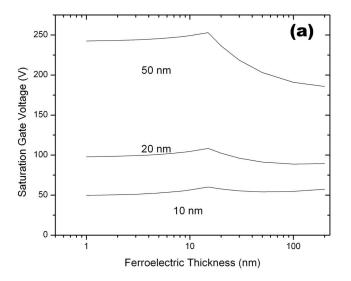

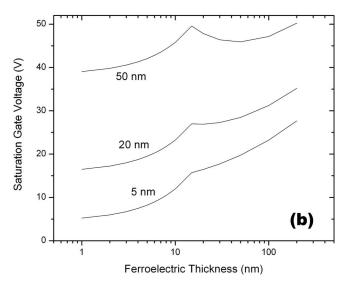

FIG. 2. The required saturation gate voltage as a function of ferroelectric film thickness for different thicknesses of silicon oxide (a) and hafnium oxide (b).

tric film, and can be determined by inserting the saturation values,  $P_S$  and  $E_S$  into Eq. (1) to yield the following expression:

$$V_{\rm GB}^{\rm S} = \Phi_{\rm MS} + \frac{\varepsilon_0 \varepsilon_f E_S}{C} + \frac{P_S d_i}{\varepsilon_0 \varepsilon_i} + 2 \phi_F. \tag{7}$$

The saturation field of the ferroelectric film  $E_S$  is conservatively set at 150% of the nominal coercive field  $E_C$ , the half width of the hysteresis loop. While the polarization and dielectric constant are insensitive to thickness, the coercive field depends strongly on thickness, ranging from 50 MV/m in thick films, to 500 MV/m in films of 15 nm or thinner. The device operation voltage, therefore, depends on both the ferroelectric film thickness and the thickness and dielectric constant of the insulating layer. This is illustrated in Fig. 2 for two insulators. For silicon oxide  $[\varepsilon_i=3.9, \text{ Fig. 2(a)}]$ , the saturation gate voltage is quite high, even with thickness 10 nm. For hafnium oxide  $[\varepsilon_i=25, \text{ Fig. 2(b)}]$ , the saturation voltage is significantly reduced, and is more sensitive to the thickness of the ferroelectric layer.

TABLE I. Parameters used in the model.

| Parameter                                               | Value                                              |

|---------------------------------------------------------|----------------------------------------------------|

| Silicon doping level $N_A$                              | $1 \times 10^{16} \text{ cm}^{-3} (p\text{-type})$ |

| Insulating layer dielectric constant $\varepsilon_i$    | 25 (hafnium oxide)                                 |

|                                                         | 3.9 (silicon oxide)                                |

| Insulating layer thickness $d_i$                        | 10 nm                                              |

| Ferroelectric layer dielectric constant $\varepsilon_f$ | 10                                                 |

| Ferroelectric layer saturation polarization $P_S$       | $0.1 \text{ C/m}^2$                                |

| Ferroelectric layer remanent polarization $P_R$         | $0.09 \text{ C/m}^2$                               |

| Ferroelectric layer coercive field $E_C$                | 125 MV/m                                           |

| Ferroelectric layer thickness $d_f$                     | 20 nm                                              |

### III. MODEL APPLICATION TO FERROELECTRIC COPOLYMER FILMS

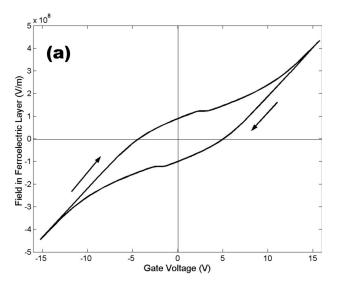

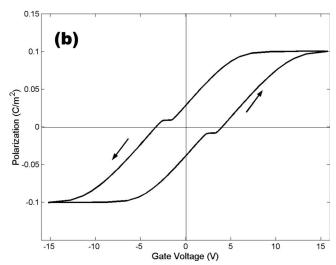

In this section, the model developed by Miller and McWhorter<sup>9</sup> will be applied to investigate a particular MFIS device involving a 20-nm-thick PVDF copolymer film. The model takes into account the properties of the ferroelectric copolymer LB films, <sup>6,16,18</sup> as summarized in Table I. A nominal coercive field of 125 MV/m suffices, and the remainder of the modeling will use this value. The hysteresis loop for the ferroelectric layer (Fig. 1) is difficult to measure directly in MFIS structures but it is readily extracted from the model as shown in Fig. 3(a), where the field in the ferroelectric film reached a maximum of 450 MV/m (or about 2.6 times the coercive field) in the accumulation mode. Because of the hysteresis in this field plot, a significant field exists in the ferroelectric layer even at zero gate bias. This zero-bias field tends to destabilize the polarization state and thus it is referred to as the "depolarization field." The depolarization field arises because the oxide or semiconductor that is in direct contact with the ferroelectric cannot provide enough charges to fully compensate for the surface charge of the polarized ferroelectric. The depolarization field is the cause for the reduced remanent polarization evident in a narrowing of the hysteresis loop shown in Fig. 3(b), compared to the one from the simple MFM capacitor (Fig. 1), where the metal electrodes (ideally) provide complete compensation of the polarization. The depolarization field in the MFIS is larger after saturating the sample in strong inversion (125 MV/m) with positive gate bias than in accumulation (100 MV/m) with negative gate bias and therefore the MFIS should be slightly more stable in the negative-bias polarization state. The depolarization field will tend to further reduce film polarization and consequently reduce the capacitance hysteresis over time, making the states less distinct. Film depolarization is therefore an important issue in state retention. It should be noted that this model assumes that electrostatic steady state is always established within the device structure. This may not be the case if higher ramp rates are used and the ferroelectric film (or semiconductor surface charge) is not given enough time to come to equilibrium. In those situations, minority carriers in inversion mode may not respond to the applied signal and the remanent polarization would be reduced. That is, the finite minority carrier response time or polarization switching time, or both, will tend to shrink the memory window under high-speed operation.<sup>19</sup>

FIG. 3. State of the ferroelectric layer in the MFIS as the gate voltage is cycled: (a) electric field; (b) electric polarization.

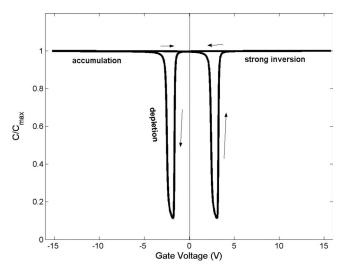

The capacitance-voltage curve (Fig. 4) of the MFIS structure reveals the same features as those seen in a typical capacitance-voltage hysteresis loop for a metal-oxide-semiconductor device but with hysteresis due to the switch-

FIG. 4. Capacitance-voltage hysteresis of an MFIS capacitor.

able polarization of the ferroelectric. (If the capacitance is measured at a frequency higher than the reciprocal minority carrier response time, then the capitance stays low in inversion, as is often observed.<sup>6,10</sup>) Because of this hysteresis, the value of the flat band (the point where the silicon surface potential is zero) and threshold (boundary between depletion and inversion) voltages depends on the electrical history of the sample. The amount of hysteresis is quantified by the horizontal voltage shift, called the "memory window," where the maximum memory window is achieved when the polarization is saturated in both states. The maximum width of the memory window  $\Delta V_{\text{TH}} = 2E_C d_F$  depends only on the properties of the ferroelectric layer. For the capacitance hysteresis loop in Fig. 4, which was obtained with a coercive field of 125 MV/m and ferroelectric film thickness of 10 nm, the memory window is 5 V. Although hysteresis is clearly shown in the C-V characteristics of the modeled MFIS capacitor, it is more difficult to achieve a significant zero gate bias on/off ratio in the source-drain current of a ferroelectric field effect transistor memory because of the requirement of strong inversion mode for source-drain current. The capacitance data do show that at zero bias one of the states remains in the strong inversion mode (high source-drain conductivity) while the other remains in accumulation. Thus, the model implies a measurable, nonvolatile on/off ratio in drain current for the corresponding ferroelectric field effect transistor.

In summary, we evaluated ferroelectric polymer based gate structures and determined that an operating voltage of 12 V is expected for a fully saturated 10 nm LB ferroelectric layer on a 5 nm insulating layer with a large dielectric constant. In the case of ferroelectrics that have large coercive fields, such as PVDF and its copolymers, a large memory window is easily achieved due to the large coercive field of the copolymer but this comes at the expense of large operating voltages. The copolymer's relatively low permittivity  $(\varepsilon_f = 10)$  results in a smaller voltage drop across the buffer layer compared to perovskite ferroelectrics, which have a much higher dielectric permittivity ( $\varepsilon_f$ =250). The large remanent polarization is favorable because it can lead to higher drain-source currents in the Fe-FET structure. However, this also means that the ferroelectric cannot be fully polarized with low voltage operation, and less-stable subloops are present. Regarding the dielectric layer, it should have a high permittivity and breakdown field so that the ferroelectric can be polarized as much as possible without experiencing breakdown. This extra dielectric layer can reduce the current

density through the capacitor stack and prohibit charge injection, particularly if the semiconductor and ferroelectric band gaps are a mismatch; but it separates the ferroelectric polarization from the compensation charge in the semiconductor, which is limited even without the buffer layer. Since both the properties of the ferroelectric and insulating layers prohibit saturation at low voltages in field effect devices based on ferroelectric polymers, much attention should be given to the retention times in such structures. It is interesting to note that a saturation voltage of 6 V has been achieved for a MFIS consisting of a 100 nm 77/23 copolymer spun film on a 3 nm Ta<sub>2</sub>O<sub>5</sub> insulator with approximate dielectric constant of 25.<sup>5</sup>

#### **ACKNOWLEDGMENTS**

This work was supported by the National Science Foundation (Grant No. ECS-0600130) and by the Nebraska Research Initiative.

<sup>1</sup>K. Tashiro, in *Ferroelectric Polymers*, edited by H. S. Nalwa (Dekker, New York, 1995), pp. 63–181.

<sup>2</sup>T. Nakajima, Y. Takahashi, S. Okamura, and T. Furukawa, Jpn. J. Appl. Phys. 48, 09KE04 (2009).

S. H. Lim, A. C. Rastogi, and S. B. Desu, J. Appl. Phys. 96, 5673 (2004).

G. H. Gelinck, A. W. Marsman, F. J. Touwslager, S. Setayesh, D. M. de Leeuw, R. C. G. Naber, and P. W. M. Blom, Appl. Phys. Lett. 87, 092903 (2005).

<sup>5</sup>S. Fujisaki, H. Ishiwara, and Y. Fujisaki, Appl. Phys. Lett. **90**, 162902 (2007).

<sup>6</sup>T. J. Reece, S. Ducharme, A. V. Sorokin, and M. Poulsen, Appl. Phys. Lett. 82, 142 (2003).

R. Schwartz, J. Kirkness, and P. Smith, J. Appl. Phys. 100, 5 (2006).

S. L. Miller, J. R. Schwank, R. D. Nasby, and M. S. Rodgers, J. Appl. Phys. 70, 2849 (1991).

<sup>9</sup>S. L. Miller and P. J. McWhorter, J. Appl. Phys. **72**, 5999 (1992).

<sup>10</sup>E. H. Nicollian and J. R. Brews, MOS Physics and Technology (Wiley, New York, 1982).

<sup>11</sup>S. L. Miller, R. D. Nasby, J. R. Schwank, M. S. Rodgers, and P. V. Dressendorfer, J. Appl. Phys. 68, 6463 (1990).

<sup>12</sup>L. S. Berman, Semiconductors **35**, 193 (2000).

<sup>13</sup>J.-M. Sallese and V. Meyer, IEEE Trans. Electron Devices 51, 2145 (2004)

<sup>14</sup>M. Liu, H. K. Kim, and J. Blachere, J. Appl. Phys. **91**, 5985 (2002).

<sup>15</sup>H.-T. Lue, C.-J. Wu, and T.-Y. Tseng, IEEE Trans. Electron Devices **49**, 1790 (2002)

<sup>16</sup>S. Ducharme, S. P. Palto, and V. M. Fridkin, in *Ferroelectric and Dielectric Thin Films*, edited by H. S. Nalwa (Academic, San Diego, 2002), Vol. 3, pp. 545–591.

<sup>17</sup>S. Ducharme, V. M. Fridkin, A. V. Bune, S. P. Palto, L. M. Blinov, N. N. Petukhova, and S. G. Yudin, Phys. Rev. Lett. 84, 175 (2000).

<sup>18</sup>S. Ducharme, T. J. Reece, C. M. Othon, and R. K. Rannow, IEEE Trans. Device Mater. Reliab. 5, 720 (2005).

<sup>19</sup>T. Furukawa, S. Kanai, A. Okada, Y. Takahashi, and R. Yamamoto, J. Appl. Phys. **105**, 061636 (2009).